# STEREO IMPACT

## PROBLEM REPORT PR-1036 SEP LVPS 2005-02-27

| 7xxx=Keil, 8xxx=ESTEC,               |                                                     | xx=GSFC/SEP, 5xxx=GSFC/ | Mag, 6xxx=CESR,      |

|--------------------------------------|-----------------------------------------------------|-------------------------|----------------------|

| Assembly : SEP                       | LVPS                                                | SubAssembly : 7         | Fop and Middle Board |

| Component/Part                       | t Number:                                           | Serial Number: I        | FM2 and FM1          |

| SEP_TOP_F001                         | and SEP_Middle_F001                                 |                         |                      |

| <b>Originator: Seld</b>              | a Heavner                                           | Organization: U.        | C. Berkeley          |

| <b>Phone : 510-643</b> -             | -8640                                               | Email : selda@ss        | 1.berkeley.edu       |

|                                      |                                                     |                         |                      |

| Failure Occurred<br>√Functional test | <b>During (Check one</b> √)<br>□ Qualification test | □ S/C Integration       | □ Launch operations  |

**Problem Description**

i di

SEP LVPS FM2 was intermittently consuming high current at turn-on. The high-current at turn-on did not reach 0.90A which is the recommended current limit for the bench supply. It typically remained at 580-600mA range. The 28V line did not change when the Supply was consuming 580mA and remained at 28.0V. The supply was not left in the high current state for longer than 30 seconds. The high-current at turn on caused some of the transistors to heat excessively. The conformal coating around the transistors and the shrink tubing covering the ferrite beads were burnt due to excessive heat

generated by the transistors.

.F

## **Analyses Performed to Determine Cause**

SEP ETU Unit was tested using the bench supply from Caltech KIKUSUI PMC35-1A. SEP ETU was turned on and off until the problem was reproduced. When the high-current occurred the switching FETS became extremely hot. The FETs were still functional after leaving the high-current on a long time. Therefore, the problem is with the FET drivers (for the switching FETs that drive the transformers). When the drivers first come on they set their output to high impedance until their supply voltage exceeds some threshold. So the FET gate floats, and depending on leakage currents the FET can turn on providing a low impedance short (through the transformer windings) on the primary regulator. This in turn causes the voltage regulator to go into current limit so the voltage never gets over the turn-on threshold for the FET driver. So the difference between supplies (and between bench supplies that come up slower or faster) is if the leakage current is large enough to charge up the gate before the primary regulator voltage gets high enough to turn on the driver.

| , Corrective Action/ Resolution |        |             |         |  |

|---------------------------------|--------|-------------|---------|--|

| √Rework                         | Repair | 🗆 Use As Is | 🗆 Scrap |  |

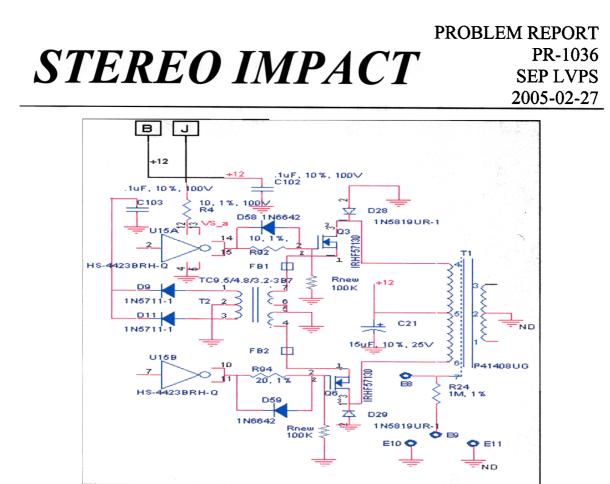

100K $\Omega$  resistor from the FET gate to ground can hold the FETs off when the driver is in high impedance mode. This solution was incorporated on ETU and the problem could not be reproduced. Figure 1 indicates where the new resistors (Rnew) will be connected for the Top and Middle Board. Please see PFR 1036 addendum for detailed instructions.

Figure 1: Additional resistors on FET drivers

Date Action Taken:

Retest Results:

Corrective Action Required/Performed on other Units: √Serial Number(s):SEP LVPS ETU

## **Closure Approvals**

| Subsystem Lead:<br>IMPACT Project Manager:<br>IMPACT QA: | Date:<br>Date<br>Date:<br>Date: |

|----------------------------------------------------------|---------------------------------|

| NASA IMPACT Instrument Manager:                          | Date:                           |

Date: March 8, 2005

## **STEREO SEP LVPS MIDDLE BOARD PFR 1036 INSTRUCTIONS**

ASSEMBLY NUMBER: \_FMI

Requesting Engineer: Selda Heavner

## 1. Corrective Action for MIDDLE BOARD

1) Bake the boards at 60°C.

Completed by: <u>H7</u>

Start Time:  $\underline{500}\underline{M}$  Stop Time:  $\underline{800}\underline{M}$ Completed by:  $\underline{M}\underline{\gamma}$  Date:  $\underline{3-8.9}$ . -05

2) Remove transistors with reference designators Q3, Q6, Q14, Q11, Q22, Q15, Q18, and Q20 (IRHF57130SCS) from the middle board. Do NOT use metallic tools to remove conformal coating.

2a) Remove the two wires interconnecting the two boards of Completed by: <u>N/A</u> Date: <u>March 8</u>, 2005 3-11-6C

3) Remove burnt shrink tubing covering the ferrite beads. Record the location of removed ferrite beads.

No burnt transistors, shvink tubing SSH

Completed by: SSH

Date: March 8,2005

4) Remove burnt wires. Record the location of removed wires.

no burnt wires

Completed by: <u>SSH</u> Date: <u>Maych</u> 8,200

5) Remove 1N6642 diodes with reference designator D58, D59, D60, D62, D64, D65, D66, D68 Do NOT use metallic tools to remove conformal coating over the diod

Completed by:  $\underline{HY}$ Date: 3 -/4-05

7) Prepare 8 100K (RNC50H1003FR) resistors on bench prior to soldering by cutting one side of the resistor's lead short and connecting #24AWG stranded insulated wire with lash splice. Use #30AWG bus wire to perform lash splice. The other lead will connect directly on the diode anode side. Have the lash splice inspected before putting shrink tubing over the lash splice.

Da

| ate: |                                                                                                                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Completed by: $\frac{44}{7}$ Date: $\frac{3-15-0}{5}$                                                                                                                   |

|      | QA Inspection by: Date: Date:                                                                                                                                           |

|      | GSFC Inspection by: Mento Moder 3/12/05                                                                                                                                 |

| 8)   | Install ferrite beads (BDS3.5/1.3/3.3/4S2) on Q3, Q6, Q11, Q18, Q14 and Q15 (Do NOT Install on Q20 and Q22. Their ferrite beads are installed on current transformers). |

| 9)   |                                                                                                                                                                         |

|      | Completed by: $N/A$ Date: $3-21-05$                                                                                                                                     |

| 10   | ) Put shrink tubing around the ferrite beads that were removed at item #2                                                                                               |

|      | Completed by: $\frac{N/A}{Date}$ Date: $3-21-05$                                                                                                                        |

|      |                                                                                                                                                                         |

11) Solder the wires on the board that were removed at item #3.

Completed by: \_N/A Date: 3-21-05

12) Record D/C of the 100K (RNC50H1003FR) resistors.

D/C: 98 Completed by:

13) Plug new D58 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

d/c:<u>H987</u> D58: JANTXV1N6642 Date: 3-17-05 Completed by: \_\_\_\_\_\_

14) Connect the 100K resistor (lead side) on the anode side of D58 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>H</u>

Date: 3-//

Date:

15) Install a post on E10.  $\mathbb{Z}^{9}$

Completed by: \_\_\_\_\_\_

Date: <u>3-/ 7</u>-

16) Connect the other side of the 100K resistor to E10.

Date: 3-17-00 Completed by: <u>H</u>

17) Plug new D59 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D59: JANTXV1N6642

Completed by: <u>H</u>

D/C:<u>H984</u>7 Date: 3-17-05

18) Connect the 100K resistor (lead side) on the anode side of D59 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: /////

Date: <u>3-17-05</u>

19) Connect the other side of the 100K resistor to E10.

Completed by: <u>H</u>

Date: 3-/2-25 to the resistor using bus wire #32 AWG. SSH 20) Plug new D60 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D60: JANTXV1N6642

D/C: <u>H484</u> Nate: <u>3-17-05</u>

Completed by: \_\_\_\_\_\_

21) Connect the 100K resistor (lead side) on the anode side of D60 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Date: 3-17-0(

22) Install a post on E22 E2

Completed by: \_\_\_\_\_\_

Date: <u>3-17-05</u>

23) Connect the other side of the 100K resistor to E22. E21

E21 & EZZ must remain connected. Connect EZI&EZZ to the resistar susing his wire #327009 SSTI 3-21-05 3-21-05

E10 \$ E9 must remain

Completed by: <u>H7</u>

- Date: 3 17 05

- 24) Plug new D62 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do **NOT** cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D62: JANTXV1N6642

D/C: <u>H984</u> Date: 3-12-05 Completed by: <u>H</u>

25) Connect the 100K resistor (lead side) on the anode side of D62 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: \_\_\_\_\_\_\_

Date: <u>H787</u>7

26) Connect the other side of the 100K resistor to E22.

Completed by:

Date: 317-00

27) Plug new D64 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board, Record D/C below.

D64: JANTXV1N6642

Completed by: <u><u>H</u><u></u> Date: <u>3-17-05</u></u>

D/C: <u>H484</u>/

28) Connect the 100K resistor (lead side) on the anode side of D64 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Date: 3-17-0(

Completed by: \_\_\_\_\_\_

29) Install a post on E44.

Completed by: <u>H7</u> Date: <u>3-17-05</u> 30) Connect the other side of the 100K resistor to E44. <u>E41</u> Completed by: <u>H7</u> Date: <u>3-17-05</u> Date: <u>3-17-05</u> Date: <u>3-17-05</u> Date: <u>3-17-05</u> Wire #32twg. <u>3-21-05</u> SSH

31) Plug new D65 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. 7/3-21-05 Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D65: JANTXV1N6642

Completed by: <u>H7</u>

D/C: <u>H 48</u>

Date:

32) Connect the 100K resistor (lead side) on the anode side of D65 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Date: 3 - 7 - 0 - 0Completed by: \_\_\_\_\_

33) Connect the other side of the 100K resistor to E44.

Date: 3-17-0 Completed by: \_\_\_\_\_

34) Plug new D66 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D66: JANTXV1N6642

D/C:<u>H9877</u> Completed by: <u>Hy</u> Date: <u>3-12-05</u>

35) Connect the 100K resistor (lead side) on the anode side of D66 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>H</u>Y Date: <u>3-17-0</u>

36) Install a post on E52. Z

Completed by:  $\underline{H\gamma}$

Date: <u>3-17-05</u> E52&E51 must remain Connected, Connect E52 and E51 to the resistor Using a bus wine #32Awg SSH

37) Connect the other side of the 100K resistor to E52.

Completed by: \_\_\_\_\_

38) Plug new D68 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. Do **NOT** cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board on the board on the board. Record D/C below.

D68: JANTXV1N6642 D/C: <u>1984</u>

Completed by: <u>H7</u>

- Date: 3-17-05

- 39) Connect the 100K resistor (lead side) on the anode side of D69 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>HY</u>

Date: <u>3-17-05</u>

40) Connect the other side of the 100K resistor to E52.

Completed by: \_\_\_\_\_

41) Thoroughly clean the board.

Completed by: <u>H</u>

Date:  $3 - 7 - 0 \int$

|                                          | QA Inspector | GSFC Inspector    |

|------------------------------------------|--------------|-------------------|

| Solder Inspection                        | 3-21-05      |                   |

| Part Orientation                         | Der 1        |                   |

| Layout                                   |              |                   |

| Installation                             |              |                   |

| QA Inspection by:<br>GSFC Inspection by: | Date         | e: <u>3-21-05</u> |

42) Apply staking material (Uralane 5753) to all additional resistors per NASA-STD-8739.1

200 per

Mix ratio: <u>1-20-05</u> Expiration Date: <u>105</u> Start Time: <u>Scopper (bake)</u> Stop Time: <u>Scopper</u> <u>60</u> Completed by: <u>17</u> Date: <u>3-22-05</u>

43) Apply staking material on the wires per NASA-STD-8739.1

Completed by: \_\_\_\_\_\_

Date: <u>'3-22-2(</u>

44) Stake the ferrite beads on the transistor leads and the transistors (tri-star stake) per NASA-STD-8739.1

Completed by: <u>H</u>\_\_\_\_\_

- Date:

- 45) Conformally coat all new diodes, resistors and the transistors using Uralane 5750.

Completed by: \_\_\_\_\_\_

Date: 3-33.24-05

46) Take pictures of the completed rework/repair.

Completed by: \_\_\_\_\_

Date:

4

| Approved by:        | - 1994 - 4<br>- 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 | Date: |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|--|

| Approved by:        | -                                                                                                                             | Date: |  |

| QA Inspection by:   |                                                                                                                               | Date: |  |

| GSFC Inspection by: |                                                                                                                               | Date: |  |

4

- 2. Corrective Action for TOP BOARD

- Remove transistors with reference designators Q10, Q12, Q19 and Q21 (IRHF57130SCS) from 1) the top board. Do NOT use metallic tools to remove conformal coating.

Completed by: <u>N/A</u> Date: <u>03/14/05</u>

2) Remove burnt shrink tubing covering the ferrite beads. Record the location of removed ferrite beads.

no hunt shrink tubing

Completed by: <u>N/A</u>

Date: 03/14/05

3) Remove burnt wires. Record the location of removed wires.

no burnt wills

Completed by: <u>N/</u>A

Date: 03/14/05.

4) Remove 1N6642 diodes with reference designato D67 D69 D61 and D63 Do NOT use metallic tools to remove conformal coating over the diodes

Completed by:  $\underline{HY}$

Date: 3-14-0

5) Top board must be inspected by QA.

Completed by:

Date: 3-14-05

6) Prepare 4 100K (RNC50H1003FR) resistors on bench prior to soldering by cutting one side of the resistor's lead short and connecting #24AWG stranded insulated wire with lash splice. Use #30AWG bus wire to perform lash splice. The other lead will connect directly on the diode anode side. Have the lash splice inspected before placing shrink tubing

| 7) | ) Completed by: $H\gamma$ Date: $3-45-65$                                              |

|----|----------------------------------------------------------------------------------------|

|    | QA Inspection by: Date: Date:<br>QA Inspection by: /////////////////////////////////// |

|    | Linstall ferrite beads (BDS3 5/1 3/3 3/4S2) on O10, O12, O19 and O21                   |

| 0, | Completed by: Date: N/A 3-21-05                                                        |

Date:

١.

| (ke) Solder transistors Q10, Q12, Q                                                                                    | 19 and Q21 on the board                          |                                                                            |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|

| Oompleted by:                                                                                                          |                                                  |                                                                            |

| opinipieted by                                                                                                         | Duto                                             |                                                                            |

| 10) Put shrink tubing around the fe                                                                                    | rrite beads that were removed                    | at item #2                                                                 |

| Completed by:                                                                                                          | Date:                                            | N/0 A 2-21.05                                                              |

| 11) Solder the wires on the board t                                                                                    | that were removed at item #3.                    | N/A 1-3-21-05                                                              |

| Completed by:                                                                                                          | Date:                                            |                                                                            |

| 12) Record D/C of the 100K (RNC                                                                                        | 50H1003FR) resistors.                            |                                                                            |

| D/C:                                                                                                                   | $\langle \rangle$                                |                                                                            |

| Completed by:                                                                                                          | Date:                                            |                                                                            |

|                                                                                                                        |                                                  |                                                                            |

| <ol> <li>Plug new D67 on its pads. Do<br/>Do <u>NOT</u> cut the leads of the d<br/>board. Record D/C below.</li> </ol> | • <u>NOT</u> SOLDER until the resistor is placed | or is connected on the anode side.<br>I (not soldered) on the board on the |

| D67: JANTXV1N6642                                                                                                      | d/c: <u>#9877</u>                                |                                                                            |

| Completed by:                                                                                                          | Date: <u>3-17-</u>                               | es                                                                         |

| 14) Connect the 100K resistor (lea anode (leaving at least 2x lead                                                     | ad side) on the anode side of D                  | 67 and loop the resistor around the<br>e diode lead. Solder the diode lead |

| Completed by:                                                                                                          | Date: <u>3-17-</u>                               | E56 \$ E55 must remain                                                     |

| 15) Install a post on E56. こ                                                                                           |                                                  | E56 & E55 must remain<br>connected. Connect the resistor                   |

| Completed by:                                                                                                          | Date: <u>3-17-</u>                               | to E56 (or E55) using #32<br>The bus wire. SSH                             |

16) Connect the other side of the 100K resistor to E56.

Completed by: \_// //\_\_\_

Date: 3-17-05

17) Plug new D69 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. Do <u>NOT</u> cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D69: JANTXV1N6642

Completed by: HY

D/C: <u>H 9877</u> Date: <u>3-17-05</u>

18) Connect the 100K resistor (lead side) on the anode side of D69 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Date: 3-17-05 Completed by: \_\_\_\_\_\_

19) Connect the other side of the 100K resistor to E56.

Completed by: <u>H</u> Date: <u>3-17-05</u>

20) Form a pigtail on D61 anode. Solder D61. Record D/C below.

DIC: <u>M984</u>7 D61: JANTXV1N6642 Date: 3-17-05 Completed by: <u>H</u>

21) Connect the 100K resistor (lead side) on the anode side of D61 and loop the resistor around. Solder the diode the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u><u>H7</u> Date: <u>3-17-05</u></u>

22) Install a post on E32. E3D

Completed by: \_\_\_\_\_\_

Date: 3-17-05 E32 & E30 must remain

23) Connect the other side of the 100K resistor to E32.

Completed by: <u>H7</u>

ESQUEDU INTER

H22

24) Plug new D63 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board, Record D/C below.

D63: JANTXV1N6642

Completed by: \_\_\_\_\_\_

D/C: <u>H984</u> Date: <u>3--/7-05</u>

25) Connect the 100K resistor (lead side) on the anode side of D63 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>H7</u> Date: <u>377-01</u>

26) Connect the other side of the 100K resistor to E32.

Date: 3-17-05 Completed by: <u>H7</u> 27) Thoroughly clean the board. Completed by:  $\underline{HY}$ **QA** Inspector **GSFC** Inspector **Solder Inspection** 3-21-05 **Part Orientation** Layout Installation Date: 3-21-05 **QA Inspection by: QA Inspection by:** Date:

28) Apply staking material (Uralane 5753) to all additional resistors per NASA-STD-8739.1.

Mix ratio: 1 - 20 - 05Start Time:  $\frac{1}{5} - 20 - 05$ Expiration Date: <u>506(</u> Stop Time: <u>StopAm(3-23-05)</u> bake 600° Date: 3 -22-0 Completed by:

29) Apply staking material on the wires per NASA-STD-8739.1

Completed by: <u>Hy</u> Dat

- Date: 3-22-05

- 30) Stake the ferrite beads on the transistor leads and the transistors (tri-star stake) per NASA-STD-8739.1

Completed by:

Date:

31) Conformally coat all new diodes, resistors and the transistors using Uralane 5750.

Date: 3-23-24-05 Completed by: <u>Hy</u>

32) Take pictures of the completed rework/repair.

Completed by:

Date:

Date:

۴,

•

| Approved by:      | - | Date:   |  |

|-------------------|---|---------|--|

| Approved by:      | _ | Date:   |  |

| QA Inspection by: |   | _ Date: |  |

## Date:

3.

١,

|    | rective Action for all Board with Repard<br>Add more points of staking along the re<br>NASA-STD-8739.1 | airs<br>pair wires especially where the wire changes direction per |

|----|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | Completed by:                                                                                          | Date:                                                              |

| 2) | Make sure all transistors have tri-star st                                                             | ake.                                                               |

|    | Completed by:                                                                                          | Dațe:                                                              |

| 3) | Apply staking to the leads of any transis to the transistors.                                          | stors that are in dead-bug position. Apply tri-star staking        |

|    | Completed by:                                                                                          | Date:                                                              |

| 4) | Apply more staking to the capacitors pe                                                                | er NASA-STD-8739.1                                                 |

| ., | Completed by:                                                                                          | Date:                                                              |

|    | Completed by.                                                                                          |                                                                    |

| 5) | Apply staking fillets to any parts that an                                                             | e laying on the board.                                             |

|    | Completed by:                                                                                          | Date:                                                              |

| 6) | Apply more staking to the wires that co                                                                | nnect the thermistor to the top board (SLH and TH)                 |

|    | Completed by:                                                                                          | Date:                                                              |

| 7) | Apply more staking to the wires that lay OP_HTR_RTN.                                                   | y between J1 connector and the OP_HTR and                          |

|    | Completed by:                                                                                          | Date:                                                              |

|    |                                                                                                        |                                                                    |

| 8) | Apply more staking to the wires of the                                                                 | inductors and transformers.                                        |

|    | Completed by:                                                                                          |                                                                    |

| 9) | Apply staking to cambion pins on top b                                                                 | ooard.                                                             |

|    | Completed by:                                                                                          |                                                                    |

Date:

| Approved by:        | Date: |

|---------------------|-------|

| Approved by:        | Date: |

| QA Inspection by:   | Date: |

| GSFC Inspection by: | Date: |

1. Due to insufficient boards space the resistor jumper wires are currently staked above the PCB surface area forming a bridge along the side and over components - DSC000053, DSC000062, DSC000072 & DSC000092. USE AS IS(I do not see any reliability issues because wires are staked loose bewteen components).

2. Two resistor leads insulated with shrink tubing, staked over three surface mount resistors that are covered with conformal coat material FM1- DSC00010 & DSC00011. USE AS IS (I do not see any reliability issues with FM2 resistors wire are insulated with kapton tape to prevent shorting.

3. Bridging staking material around transistor leads - DSC000042 & DSC000092. Rework by removing staking material from lead.

4. Resistor jumper wire mounted under the transistor package, forming a potential short - DSC000072 & DSC000082. Repair by adding staking material along the side of the transistor to protect and support jumper wire against exposure to short.

5. Cleanliness testing

All PCB's shall be tested prior 'o conformal coating.

Two basic test methods are recommended. a. resistivity of solvent extract b. Sodium chloride salt equivalent ionic contamination test USE AS IS - all boards are cleaned using Isopropyl Alcohol and dried prior to adding staking and conformal coating. Ron

## Mike Jones, 05:26 PM 3/11/2005 -0500, Wire removal

Delivered-To: ronj@apollo.ssl.berkeley.edu Date: Fri, 11 Mar 2005 17:26:46 -0500 To: ronj@ssl.berkeley.edu From: Mike Jones <mijones@pop700.gsfc.nasa.gov> Subject: Wire removal Cc: Ricardo.Rodriquez@honeywell-tsi.com, lgibb@pop400.gsfc.nasa.gov, Lil Reichenthal <lreichen@pop700.gsfc.nasa.gov> X-CanltPRO-Stream: admin X-Spam-Score: 0 () X-Scanned-By: Canlt (www . canit . ca)

Ron,

Both Larry and myself agree with the decision to remove the two wires interconnecting the two boards to allow for ease of rework. And, later to reinstall at a later time in the PR instructions. Please red line your PR instructions (sign /date redline).

Thanks, Mike Jones Delivered-To: ronj@apollo.ssl.berkeley.edu X-ASG-Debug-ID: 1111166069-15872-92-0 X-Barracuda-URL: http://mailwall.ssl.berkeley.edu:8000/cgi-bin/mark.cgi Date: Fri, 18 Mar 2005 12:14:22 -0500 To: "Lillian S. Reichenthal" <Lillian.S.Reichenthal@nasa.gov>, David Curtis <dwc@ssl.berkeley.edu>, ronj@ssl.berkeley.edu From: Mike Jones <mijones@pop700.gsfc.nasa.gov> X-ASG-Orig-Subj: Re: Fwd: SEP visual rejection items by GSFC. Subject: Re: Fwd: SEP visual rejection items by GSFC. Cc: lgibb@pop400.gsfc.nasa.gov, Laurie Kleppin <lkleppin@pop300.gsfc.nasa.gov>, Ricardo.Rodriguez@honeywell-tsi.com, "Rodriguez, Ricardo G" < Ricardo.Rodriguez@honeywell-tsi.com> X-Virus-Scanned: by Barracuda Spam Firewall at ssl.berkeley.edu X-Barracuda-Spam-Score: -5.40 X-Barracuda-Spam-Status: No, SCORE=-5.40 using global scores of TAG\_LEVEL=1.0 QUARANTINE\_LEVEL=3.0 KILL\_LEVEL=1000.0 tests=BAYES 00 X-Barracuda-Spam-Report: Code version 2.64, rules version 2.1.1942 Rule breakdown below pts rule name description -5.40 BAYES 00 BODY: Bayesian spam probability is 0 to 1% [score: 0.0000] X-Qmail-MasqDomain: False

Dave, Ron, and Lil,

Item #1 and #3 should be fine, recommend approval (valid findings).

Item #2 related photograph concerns me greatly.

I agreed that the leads could be used as terminals. However, the attaching conductor should have been in contact with the base, the pad in your case (standard practice). The way these conductor leads are at the end of the lead (terminal) brings much concern about lead fatigue (where solder joint to lead interfaces). Also, the shrink tubing is very short on the one side raising shorting concerns.

Currently, I do not recommend using as is. Need additional information from your team.

Please call, we need to talk/work this issue.

Regards, Mike Jones 301-286-3198 X-Sender: dwc@apollo.ssl.berkeley.edu Date: Thu, 17 Mar 2005 14:31:59 -0800 To: Lillian Reichenthal <lreichen@pop700.gsfc.nasa.gov> From: David Curtis <dwc@ssl.berkeley.edu> Subject: Fwd: SEP visual rejection items by GSFC. Cc: Ron Jackson <ronj@ssl.berkeley.edu> X-Proofpoint-Spam-Details: rule=notspam policy= score=0 mlx=-1 adultscore=0 adjust=0 engine=2.5.0-05031400 definitions=2.5.0-05031700

Lil:

The inspector rejected the FM2 SEP LVPS board for 3 issues listed below (see also attached pictures). Let me know if you want it written up on a PFR form. He agreed that these are really cosmetic, but wanted an official waiver. I authorized the board to proceed to conformal coat as is, with an MRB to run in parallel. I apologize for the focus on picture 17; it shows the splice of the resistor to the diode lead, the concern being how high the diode lead extends above the board. Picture 18 shows the poor strain relief (diode in the back). The other end of this diode has good strain relief, so we feel that there is not a real issue. Picture 18 also shows (poorly) the bridging of the diode lead by conformal coat (diode in front). It is not clear to me why this is an issue; Uralane is pliable enough that it should not impact strain relief. Dave

Delivered-To: dwc@apollo.ssl.berkeley.edu X-Sender: ronj@apollo.ssl.berkeley.edu X-Mailer: QUALCOMM Windows Eudora Version 5.0 Date: Thu, 17 Mar 2005 14:10:28 -0800 To: David Curtis <dwc@ssl.berkeley.edu> From: Ron Jackson <ronj@ssl.berkeley.edu> Subject: SEP visual rejection items by GSFC. X-Qmail-MasqDomain: True X-Qmail-MasqDomain: True

Dave,

Item #1 The stress relief bend radius shall not be less than the lead diameter per NASA-Std-8739.3

Item #2 Straight-through termination, lead protrusion exceeds max (0.090 inch) per NASA-Std-8739.3

Item #3 Conformal coating bridges stress relief areas there negating stress relief NASA-Std-8739.1

Ron Jackson UC Berkeley,Space Sciences Laboratory 7 Gauss Way MC 7450 Berkeley, CA 94720-7450 Tel: (510) 643-2625 AST:7731^29u18e3

AST:7731^29u18e3

Lillian Reichenthal STEREO Instrument Manager

NASA Goddard Space Flight Center Building 6, Room S126 Mail Code 463 8800 Greenbelt Road Greenbelt, Maryland 20771

(office) 301-286-5634 (fax) 301-286-1696 (cell) 443-745-2716

Attachment converted: Macintosh HD:DSC00018.JPG (JPEG/JWWR) (0005EA0C) Attachment converted: Macintosh HD:DSC00017.JPG (JPEG/JWWR) (0005EA0D) Part Number <u>SEPLVPS FM</u> Serial Number <u>FMI</u> Date <u>3-18-05</u>

Operator Seldg Heavier Inspector

## **APPENDIX 4:**

- 5. Post-Conformal Coat Tests:

- 5.1 Weight Measurement

Repeating tests after resistor installiou.

## Weight: N/A grams

## 5.2 Functional tests

**Presence of Output Voltages** 5.2.1

| Output Voltages           |        |        |         |           |

|---------------------------|--------|--------|---------|-----------|

| Signal name               | Min    | Max    | Output  | Unit      |

| SEPT-NS 5.3 Digital       | 5.04   | 5.57   | 5,306   |           |

| SEPT-NS 2.6 Digital       | 2.47   | 2.73   | 2.553   |           |

| SEPT-NS 5.6 Analog        | 5.32   | 5.88   | 5,643   |           |

| SEPT-E 5.3 Digital        | 5.04   | 5.57   | 5,386   |           |

| SEPT-E 2.6 Digital        | 2.47   | 2.73   | 2.549   |           |

| SEPT-E 5.6 Analog         | 5.32   | 5.88   | 5.706   | V         |

| SIT HET LET +13 Analog    | 12.35  | 13.65  | 13.47   | V         |

| SIT HET LET -13 Analog    | -13.65 | -12.35 | -13.61  | V         |

| SIT HET LET +6 Analog     | 5.70   | 6.30   | 5,937   |           |

| SIT HET LET -6 Analog     | -6.30  | -5.70  | -6,233  | V         |

| SIT HET LET 2.6V Digital  | 2.47   | 2.73   | a.513   | V         |

| SIT HET LET 3.4V Digital  | 3.23   | 3.57   | 3.313   | V         |

| SIT HET LET +5.1V Digital | 4.85   | 5.36   | 5,06    | . · · · V |

| SIT HET LET -5.2V Digital | -5.46  | -4.94  | - 5,199 | V         |

## 5.2.2 Efficiency

| Signal name              | Voltage | Current | Power (W) |

|--------------------------|---------|---------|-----------|

| SEPT-NS 5 3 Digital      | 78.     | 9       |           |

| SEPT-NS 2.6 Digital      |         |         |           |

| SEPT-NS 5.6 Analog       |         |         |           |

| SEPT-E 5.3 Digital       |         |         |           |

| SEPT-E 2.6 Digital       |         |         |           |

| SEPT-E 5.6 Analog        |         | <       |           |

| SIT HET LET +13 Analog   |         |         |           |

| SIT HET LET -13 Analog   |         |         |           |

| SIT HET LET +6 Analog    |         |         |           |

| SIT HET LET -6 Analog    |         |         |           |

| SIT HET LET 2.6V Digital |         | 5.0 B   |           |

| SIT HET LET 3.4V Digital |         |         |           |

# **STEREO IMPACT**

| PR Numbers: 1xxx=UCB<br>7xxx=Keil, 8xxx=ESTEC    | , 2xxx=Caltech/JPL, 3xxx=UMd, 4<br>, 9xxx=MPAe | xx=GSFC/SEP, 5xxx=GSFC/        | Mag, 6xxx=CESR,      |  |

|--------------------------------------------------|------------------------------------------------|--------------------------------|----------------------|--|

| Assembly : SEP                                   | LVPS                                           | SubAssembly : 7                | Top and Middle Board |  |

| Component/Part Number:                           |                                                | Serial Number: FM2 and FM1     |                      |  |

| SEP_TOP_F001                                     | and SEP_Middle_F001                            |                                |                      |  |

| <b>Originator:</b> Sele                          | la Heavner                                     | Organization: U.               | C. Berkeley          |  |

| <b>Phone :</b> 510-643-8640                      |                                                | Email : selda@ssl.berkeley.edu |                      |  |

| <b>Failure Occurred</b> $\sqrt{Functional test}$ | <b>I During (Check one</b> $$ )                | □ S/C Integration              | □ Launch operations  |  |

| •                                                | - (                                            |                                |                      |  |

| Environment when failure occurred:               |                                                |                                |                      |  |

| √Ambient                                         | □ Vibration                                    | □ Shock                        |                      |  |

| Thermal                                          | □ Vacuum                                       | Thermal-Vacuum                 | □ EMI/EMC            |  |

## **Problem Description**

SEP LVPS FM2 was intermittently consuming high current at turn-on. The high-current at turn-on did not reach 0.90A which is the recommended current limit for the bench supply. It typically remained at 580-600mA range. The 28V line did not change when the Supply was consuming 580mA and remained at 28.0V. The supply was not left in the high current state for longer than 30 seconds. The high-current at turn on caused some of the transistors to heat excessively. The conformal coating around the transistors and the shrink tubing covering the ferrite beads were burnt due to excessive heat generated by the transistors.

## **Analyses Performed to Determine Cause**

SEP ETU Unit was tested using the bench supply from Caltech KIKUSUI PMC35-1A. SEP ETU was turned on and off until the problem was reproduced. When the high-current occurred the switching FETS became extremely hot. The FETs were still functional after leaving the high-current on a long time. Therefore, the problem is with the FET drivers (for the switching FETs that drive the transformers). When the drivers first come on they set their output to high impedance until their supply voltage exceeds some threshold. So the FET gate floats, and depending on leakage currents the FET can turn on providing a low impedance short (through the transformer windings) on the primary regulator. This in turn causes the voltage regulator to go into current limit so the voltage never gets over the turn-on threshold for the FET driver. So the difference between supplies (and between bench supplies that come up slower or faster) is if the leakage current is large enough to charge up the gate before the primary regulator voltage gets high enough to turn on the driver.

| Corrective Action/ Resolution |        |             |         |  |  |

|-------------------------------|--------|-------------|---------|--|--|

| √Rework                       | Repair | 🗆 Use As Is | 🗆 Scrap |  |  |

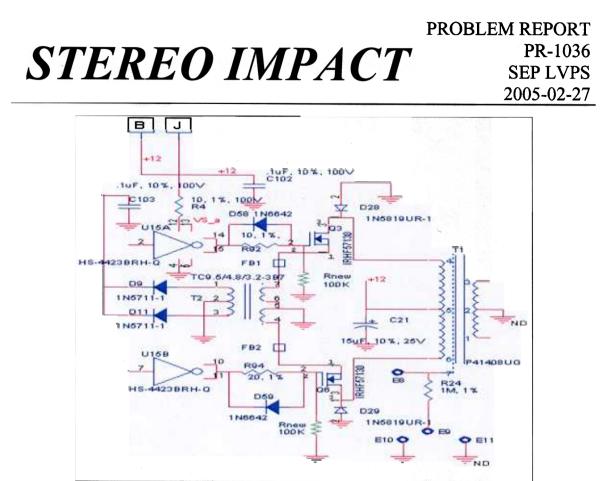

100K $\Omega$  resistor from the FET gate to ground can hold the FETs off when the driver is in high impedance mode. This solution was incorporated on ETU and the problem could not be reproduced. Figure 1 indicates where the new resistors (Rnew) will be connected for the Top and Middle Board. Please see PFR 1036 addendum for detailed instructions.

Figure 1: Additional resistors on FET drivers

Date Action Taken:

Retest Results:

Corrective Action Required/Performed on other Units:

Serial Number(s):SEP LVPS ETU

## **Closure Approvals**

| Subsystem Lead:                 | Date: |

|---------------------------------|-------|

| IMPACT Project Manager:         | Date  |

| IMPACT QA:                      | Date: |

| NASA IMPACT Instrument Manager: | Date: |

,

## STEREO SEP LVPS MIDDLE BOARD PFR 1036 INSTRUCTIONS

| AS | SEN             | IBLY NUMBER:FM2_                                                                                                                                                                                                                                                                         |

|----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Re | ques            | sting Engineer:                                                                                                                                                                                                                                                                          |

|    |                 |                                                                                                                                                                                                                                                                                          |

| 1. | <u>Co</u><br>1) | Bake the boards at 60°C. 24 hours. Total Hrs 19 Hrs 370-05                                                                                                                                                                                                                               |

|    |                 | Start Time: <u>1730 PM39</u> Stop Time: <u>8-50MM</u> 3-10                                                                                                                                                                                                                               |

|    |                 | Completed by: $\underline{H}$ Date: $\underline{10-3-05}$ , 2                                                                                                                                                                                                                            |

|    | 2)              | Remove transistors with reference designators 03,06,014,011,022,0x5,018 and 020<br>(IRHF57130SCS) from the middle board. Do <u>NOT</u> use metallic tools to remove conformal<br>coating.                                                                                                |

| 1  | da)             | remove the Two wires interconnecting the two boards 3-10-05<br>Completed by: <u>H</u> Date: <u>3-10-05</u>                                                                                                                                                                               |

|    | 3)              | Remove burnt shrink tubing covering the ferrite beads. Record the location of removed ferrite beads.                                                                                                                                                                                     |

|    |                 | wire number 2. 3 from ConnTI                                                                                                                                                                                                                                                             |

|    |                 | Completed by: $\underline{+17}$ Date: $\underline{370-05}$                                                                                                                                                                                                                               |

|    | 4)              | Remove burnt wires. Record the location of removed wires.                                                                                                                                                                                                                                |

|    |                 | No burnt wires \$ 3-10-05                                                                                                                                                                                                                                                                |

|    |                 |                                                                                                                                                                                                                                                                                          |

|    |                 | Completed by: $N/A$ Date: $3-14-0.5$                                                                                                                                                                                                                                                     |

|    | 5)              | Remove 1N6642 diodes with reference designator 058 059 060 062 064 065 066 068<br>Do NOT use metallic tools to remove conformal coating over the diodes                                                                                                                                  |

|    |                 | Completed by: $\underline{H7}$ Date: $\underline{3-10-05}$                                                                                                                                                                                                                               |

|    | 6)              | The middle board must be inspected. $M_{first} = PFR^{#} 1037$                                                                                                                                                                                                                           |

|    | bà              | The middle board must be inspected.<br>Completed by: Date: 3-14-05<br>Bake the board & 60°C - Date: Time N/A stop time N/A R                                                                                                                                                             |

|    | 7)              | Prepare 8 100K (RNC50H1003FR) resistors on bench prior to soldering by cutting one side of the resistor's lead short and connecting #24AWG stranded insulated wire with lash splice. Use #30AWG bus wire to perform lash splice. The other lead will connect directly on the diode anode |

Page 1 of 14

side. Have the lash splice inspected before putting shrink tubing over the lash splice.

## PROBLEM REPORT STEREO IMPACT SEP LVPS Middle FM1 **PR-1037** 2005-03-10

PR Numbers: 1xxx=UCB, 2xxx=Caltech/JPL, 3xxx=UMd, 4xxx=GSFC/SEP, 5xxx=GSFC/Mag, 6xxx=CESR, 7xxx=Keil, 8xxx=ESTEC, 9xxx=MPAe **Assembly : SEP LVPS** SubAssembly : Top and Middle board **Component/Part Number: SEP F001** Serial Number: FM2 and SEP Middle F001 **Originator:** Ron Jackson **Organization: UC Berkelev** Phone: (510) 643-2625 Email : ronj@ssl.berkeley.edu Failure Occurred During (Check one  $\sqrt{2}$ ) □ Qualification test X Functional test □ S/C Integration □ Launch operations **Environment when failure occurred:** □ Ambient □ Vibration □ Acoustic □ Thermal □ Vacuum □ Thermal-Vacuum **EMI/EMC Problem Description** Soldermask substrate scraped exposing top layer.

## **Analyses Performed to Determine Cause**

Soldermask damaged during conformal coating removable @ Q3 and Q6 - Top layer(1.5mils) of soldermask damaged only. Second layer of glass fiber material not damaged.

| Cor                                | rective Action/ Resolution                       |

|------------------------------------|--------------------------------------------------|

| Rework     Repair                  | Use As Is                                        |

| Cover exposed soldermask area      | s with conformal coat material to repair damage. |

| use 3M Scotch-1                    | Jeld # 1838 B/A REFEREN EN17396                  |

| Date Action Taken: 3-11-05 H-      | Retest Results:                                  |

|                                    | formed on other Units 🗆 Serial Number(s):        |

|                                    |                                                  |

|                                    | Closure Approvals                                |

| Cash av rationer 1                 |                                                  |

| Subsystem L                        |                                                  |

| IMPACT Project Man                 |                                                  |

| IMPACT                             |                                                  |

| NASA IMPACT Instrument Man         | ger: Date:                                       |

| Star hake 6:3                      | 1838 14 green Epons En 206                       |

| 600 ×12                            | 5 3388J3R partA(green) sparts                    |

| Stop SiDOAY 3/8                    | - 3413537 part B (White).                        |

|                                    |                                                  |

| File: IMPACT_PFR_template61.doc 03 | 11/05 Page H 77765                               |

Completed by: <u>HY</u> Date: 3-14-05 Date: 3-14-05 QA Inspection by: GSFC Inspection by ate: 8) Install ferrite beads (BDS3.5/1.3/3.3/4S2) on Q3, Q6, Q11 Q18, Q14 and Q15 Do NOT Install on 1/2 023 Q20 and Q22 Their ferrite beads are installed on current transformers). Ferrite beads are installed on source lead. Date: 3-15-05 Solder transistors Q3, Q6, Q14, Q11, Q22, Q15, Q18, and Q20 (IRHF57130SCS) on the board 9) Completed by: 1/7 Date: 3-15-05 inspection of Transistors will be from back side of board for source lea 9a 10) Put shrink tubing around the ferrite beads that were removed at item #2 Staking only Date: 03/14/05 SSH . 5753-B Let # HK4K 40-4646 removed at item #3. Exp: 05/05 60.049 Completed by: <u>N/A</u> 11) Solder the wires on the board that were removed at item #3. 5753-A 6+# HK4K Po-DJ180Z R Exp: 06/05 12.0599/10/0 Date: <u>3-18-05</u> Completed by: \_\_\_\_\_\_ 12) Record D/C of the 100K (RNC50H1003FR) resistors. D/C: <u>984</u> Completed by: <u>Date: 3-14-05</u> Completed by: <u>Date: 3-14-05</u> Completed by: <u>Date: 3-14-05</u> Completed by: <u>Cab-0-Sil 4.29</u> Add Start <u>3:75-0555H</u> Stop <u>3-76-05</u> *Given to nore free* Cab-0-Sil 4.29 Add Start <u>3:75-0555H</u> Stop <u>3-76-05</u> *Given to nore free* Do NOT cut the leads of the diades until the resistor is connected on the anode side. Stop <u>4</u> Do NOT cut the leads of the diades until the resistor is connected on the anode side. Stop <u>4</u> Do NOT cut the leads of the diades until the resistor is placed (not coldered) on the heard on the Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below. D58: JANTXV1N6642 H984 D/C: H984 7 Date: 3-15-05 Completed by: <u>H</u> 14) Connect the 100K resistor (lead side) on the anode side of D58 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Date: 3-15-01 Completed by: <u>H7</u>

Date:

15) Install a post on E10.

Completed by:

Date:  $3 - \sqrt{5} - \sqrt{5}$

16) Connect the other side of the 100K resistor to E10.

Completed by: <u>H</u> Date: 3-/(--

17) Plug new D59 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D59: JANTXV1N6642

Completed by: <u>H</u>

D/C: <u>1984</u>7 Date: 3-15-01

18) Connect the 100K resistor (lead side) on the anode side of D59 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

- Completed by: <u>17</u> 19) Connect the other side of the 100K resistor to E10. <u>Mass mine</u> Completed by: <u>17</u> Date: <u>375-05</u> E10 & E9 must remain Connect ed. There fore, Connect E10 to the resistor using bus wire #32Awg. <u>01 SSH</u>. 3-16-05

- 20) Plug new D60 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D60: JANTXV1N6642

Completed by: <u>H</u>

D/C:  $\frac{H484}{Date: 3-15-25}$

21) Connect the 100K resistor (lead side) on the anode side of D60 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

22) Install a post on E22.

Completed by: <u>H7</u>

Date: 3-15-05 E21 é E22 Must remain connected. Connect E21 é E22 to the resistor using bus Date: 3-15-05 Wire # 32AWG. 11-05 Stil 2 12 05

23) Connect the other side of the 100K resistor to E22.

Completed by:  $\underline{HY}$  Date:  $\underline{3-15-05}$

24) Plug new D62 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not solder n the board on the board. Record D/C below.

D/C: <u>H984</u>7

D62: JANTXV1N6642

Completed by: <u>H</u>

Date: 3-12-25 25) Connect the 100K resistor (lead side) on the anode side of DF anode (leaving at least 2x lead diameter distance) and cut th and the resistor. Note: Avoid placing the additional resistor

ind the

Completed by: \_\_\_\_\_

Date: 3-15-05

26) Connect the other side of the 100K resistor to E22.

Date: 3 - 15 - 05Completed by: <u>H</u>

27) Plug new D64 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D64: JANTXV1N6642 D/C:  $\underline{H9847}$ Completed by:  $\underline{H7}$  Date:  $\underline{3-15-05}$

28) Connect the 100K resistor (lead side) on the anode side of D64 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: 177 Date: 3-15-05

29) Install a post on E44.

Completed by: <u>H7</u> Date: <u>3-/5-05</u>

30) Connect the other side of the 100K resistor to E44.

Completed by:  $H\overline{/}$  Date:  $3\overline{/}$

31) Plug new D65 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D65: JANTXV1N6642

Completed by: \_\_\_\_\_\_

D/C: H9847 Date: 3-15-01

E44 & E41 must remain to the resistor using bus wire # 32AWG. 3-17-05 connected. Connect E21 & E22

de lead

Date:

32) Connect the 100K resistor (lead side) on the anode side of D65 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

33) Connect the other side of the 100K resistor to E44.

Completed by: \_\_\_\_\_

Date: 3 - 5 - 0 (

34) Plug new D66 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D66: JANTXV1N6642

D/C:<u>H9847</u> Completed by:  $\underline{H7}$  Date:  $\underline{346-05}$

35) Connect the 100K resistor (lead side) on the anode side of D66 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: \_\_\_\_\_\_

Date: 3-16-05

36) Install a post on E52.

Completed by: <u>H</u>

Date: 3-16-05

- E52\$E51 must remain

- 37) Connect the other side of the 100K resistor to E52.

Completed by: <u>H</u>\_\_\_\_\_ Date: <u>3-/6-05</u>

38) Plug new D68 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. <u>3-17-05</u>

38) Plug new D68 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. <u>3-17-05</u>

38) Plug new D68 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. <u>3-17-05</u>

38) Plug new D68 on its pads. Do <u>NOT</u> SOLDER until the resistor is connected on the anode side. <u>3-17-05</u>

D68: JANTXV1N6642 D/C:  $\underline{H9847}$ Completed by:  $\underline{H7}$  Date:  $\underline{3-6-05}$

Completed by: <u>H</u>

39) Connect the 100K resistor (lead side) on the anode side of D6g and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by:  $\underline{H7}$  Date:  $\underline{3-6-5}$

40) Connect the other side of the 100K resistor to E52.

41) Thoroughly clean the board.

Completed by:HZDate:3/6-05Thoroughly clean the board.Completed by:HZDate:3-17-05Completed by: \_\_\_\_\_

|                   | QA Inspector | GSFC Inspector |

|-------------------|--------------|----------------|

| Solder Inspection | 3-21-05      | Gimber hom     |

| Part Orientation  | E I          | Wigning Allow  |

| Layout            |              | thigh A high   |

| Installation      |              | Jacash Aldr    |

QA Inspection by: \_\_\_\_\_ Date: \_\_\_\_\_ GSFC Inspection by: \_\_\_\_\_ Date:

42) Apply staking material (bralane 5753) to all additional resistors per NASA-STD-8739.1.

3-22-05 Star 5753 9:0914

Mix ratio: 1/2005 Expiration Date: 5/05 Start Time: 5/00 Marke Stop Time: 8:00044 (3-23-05) bake 5:000 Marke Stop Time: 8:00044 (3-23-05) bake 60 c 60 c Date: 3-22-05 Completed by:

43) Apply staking material on the wires per NASA-STD-8739.1

Completed by: <u><u>H</u><u></u></u>

Date: 3-22-05

44) Stake the ferrite beads on the transistor leads and the transistors (tri-star stake) per NASA-STD-8739.1 Ref step # 9 7 3-23-05

Completed by: \_\_\_\_\_

Date: 3-15-05

45) Conformally coat all new diodes, resistors and the transistors using Uralane 5750.

Completed by: \_\_\_\_\_\_ Date: 3-23,24 -0[

46) Take pictures of the completed rework/repair.

Completed by:

Date:

Date:

ſ

,

.

| Approved by:        | - | Date:   | area. |  |

|---------------------|---|---------|-------|--|

| Approved by:        | 1 | Date:   |       |  |

|                     |   |         |       |  |

| QA Inspection by:   |   | _ Date: |       |  |

| GSFC Inspection by: |   | Date:   |       |  |

Date:

٩

- 2. Corrective Action for TOP BOARD

- 1) Remove transistors with reference designators Q10, Q12, Q19 and Q21, IRHF57130SCS) from the top board. Do <u>NOT</u> use metallic tools to remove conformal coating.

Completed by:  $\underline{HY}$ Date: 3-11-0

2) Remove burnt shrink tubing covering the ferrite beads. Record the location of removed ferrite beads.

no purnt shrink tubize

Completed by: \_\_\_\_\_\_

Date: <u>3-11-0</u>

3) Remove burnt wires. Record the location of removed wires.

no punt wire

Completed by: <u>H</u>

Date: 3-11-0(

4) Remove 1N6642 diodes with reference designator D67 D69 D61 and D63. Do <u>NOT</u> use metallic tools to remove conformal coating over the diodes

Completed by:  $\underline{HY}$

Date: 3 - 1/-0.0

5) Top board must be inspected by QA.

Date: 3-14-05 Completed by:

6) Prepare 4 100K (RNC50H1003FR) resistors on bench prior to soldering by cutting one side of the resistor's lead short and connecting #24AWG stranded insulated wire with lash splice. Use #30AWG bus wire to perform lash splice. The other lead will connect directly on the diode anode side. Have the lash splice inspected before placing shrink tubing

Date: 3-14-0 7) Completed by:  $H\gamma$ Date: <u>3-14-0</u> **QA Inspection by:** Rom Date: 3/ QA Inspection by 8) Install ferrite beads (BDS3.5/1.3/3.3/4S2) on Q10/Q12/Q19 and Q21.) E 237 Ferrite beads are installed on source leads of transistors, H3-16-05 Completed by: H7 Date: 3-15-05

Date:

٦

- 9) Solder transistors Q10, Q12, Q19 and Q21 on the board. Solder transistors Q10, Q12, Q19 and Q21 on the board. INSpection of the source store will be from back side of board for source lec Completed by: <u>H7</u> Date: <u>3-15-05</u> item N/A H 3-17-05 3-(6-1

- 10) Put shrink tubing around the ferrite beads that were removed at item #2 #3.

Date: 3-15-05

11) Solder the wires on the board that were removed at item #3.

Completed by: <u>M7</u> Date: 3-//

12) Record D/C of the 100K (RNC50H1003FR) resistors.

D/C: <u>784</u> Completed by: <u>H</u>Y

Completed by: <u>H7</u>

Date: 3-14

13) Plug new D67 on the pads. Do NOT SOLDER until the resistor is connected on the anode side. Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board. Record D/C below.

D67: JANTXV1N6642

Completed by: <u>H7</u>

D/C: H 984 Date: 3-16-00

14) Connect the 100K resistor (lead side) on the anode side of D67 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>17</u> Date: <u>3-18-</u> 15) Install a post on-<u>E56</u>

Completed by: <u>H7</u> Date: <u>3-15-05</u> \* E56 \* E55 must remain

connected. Connect ESb

\$E55 using #30+twee bus

16) Connect the other side of the 100K resistor to E56.

Completed by:

Date: 3

around the wire. 17) Plug new D69 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. 13-17-05 Do NOT cut the leads of the diodes until the resistor is placed (not soldered) on the board on the \$3.17-05 board. Record D/C below.

D69: JANTXV1N6642

Completed by: <u>H7</u>

D/C:<u>H 984</u> Date: 376-05

18) Connect the 100K resistor (lead side) on the anode side of D69 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: \_\_\_\_\_\_ Date: 3-16-25

Connect the other side of the 100K resistor to E56.

Completed by:  $\underline{HY}$  Date:  $\underline{3}-\underline{6}-\underline{5}$

20) Form a pigtail on D61 anode. Solder D61. Record D/C below.

D61: JANTXV1N6642

D/C: <u>H984</u>7 Date: 3-16-05 Completed by: <u>HY</u>

21) Connect the 100K resistor (lead side) on the anode side of D61 and loop the resistor around. Solder the diode the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>HY</u>

22) Install a post on E32.

Date: 3-18-05

Completed by: <u>H7</u> Date: <u>3-18-05</u> 23) Connect the other side of the 100K resistor to E32. <u>E32 & E30 must remain</u> connect the other side of the 100K resistor to E32. <u>E32 & E30 must remain</u> connect ed. Connect E32. to E30 with buswive To E30 with buswive H30AWG use shrink tubing. SSH

SSH

24) Plug new D63 on its pads. Do NOT SOLDER until the resistor is connected on the anode side. Do <u>NOT</u> cut the leads of the diodes until the resistor is placed (not soldered) on the board on the board on the board. Record D/C below.

D63: JANTXV1N6642  $D/C_{17847}$ Completed by:  $H_{7}$  Date: 3-16-05

25) Connect the 100K resistor (lead side) on the anode side of D63 and loop the resistor around the anode (leaving at least 2x lead diameter distance) and cut the diode lead. Solder the diode lead and the resistor. Note: Avoid placing the additional resistors on traces.

Completed by: <u>Hy</u>

Date: 3-16-05

26) Connect the other side of the 100K resistor to E32.

Completed by:  $H - Date: 3 - 6 - 0 \leq 5$

27) Thoroughly clean the board.

Date: 3-12-05 Completed by:  $\underline{HY}$ **QA** Inspector **GSFC** Inspector Solder Inspection 3-21-05 **Part Orientation** Layout Installation **4**7 Date: 3-21-65 QA Inspection by: QA Inspection by: Date:

28) Apply staking material (Uralane 5753) to all additional resistors per NASA-STD-8739.1.

3-22-05 Har 575 9:00AM Mix ratio: <u>1-20-05</u> Expiration Date: <u>5/05</u> Start Time: <u>Scop4(3-2205</u>) Stop Time: <u>Scop4(3-23-05</u>) have 60 c Date: 3-22-05 Completed by: <u>H7</u>

29) Apply staking material on the wires per NASA-STD-8739.1

Completed by:  $\underline{HY}$

Date: <u>3 - 22 - 0</u>

30) Stake the ferrite beads on the transistor leads and the transistors (tri-star stake) per NASA-STD-8739.1

Completed by: HT Date: 375-05

31) Conformally coat all new diodes, resistors and the transistors using Uralane 5750.

Completed by: \_\_\_\_/\_\_\_

Date: 3-23,24-0

32) Take pictures of the completed rework/repair.

Completed by:

Date:

Date:

4

i 🐒

| Date: |

|-------|

|       |

| Date: |

| Date: |

|       |

## Date:

4

۰

| 3. | airs |                                                                                                                   |                                                                                               |  |  |

|----|------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

|    | 1)   | Add more points of staking along the repair wires especially where the wire changes direction per NASA-STD-8739.1 |                                                                                               |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 2)   | Make sure all transistors have tri-star si                                                                        | take.                                                                                         |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 3)   | Apply staking to the leads of any transis to the transistors.                                                     | g to the leads of any transistors that are in dead-bug position. Apply tri-star staking tors. |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 4)   | Apply more staking to the capacitors per NASA-STD-8739.1                                                          |                                                                                               |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 5)   | ) Apply staking fillets to any parts that are laying on the board.                                                |                                                                                               |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 6)   | Apply more staking to the wires that co                                                                           | nnect the thermistor to the top board (SLH and TH)                                            |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 7)   | Apply more staking to the wires that lay OP_HTR_RTN.                                                              | between J1 connector and the OP_HTR and                                                       |  |  |

|    |      | Completed by:                                                                                                     | Date:                                                                                         |  |  |

|    | 8)   | Apply more staking to the wires of the in                                                                         | nductors and transformers.                                                                    |  |  |

|    |      | Completed by:                                                                                                     |                                                                                               |  |  |

|    | 9)   | Apply staking to cambion pins on top be                                                                           | pard.                                                                                         |  |  |

|    |      | Completed by:                                                                                                     |                                                                                               |  |  |

Date:

- e - e - 🐢

€

| Approved by:        | Date: |

|---------------------|-------|

| Approved by:        | Date: |

| QA Inspection by:   | Date: |

| GSFC Inspection by: | Date: |

Delivered-To: ronj@apollo.ssl.berkeley.edu Date: Fri, 11 Mar 2005 17:26:46 -0500 To: ronj@ssl.berkeley.edu From: Mike Jones <mijones@pop700.gsfc.nasa.gov> Subject: Wire removal Cc: Ricardo.Rodriquez@honeywell-tsi.com, lgibb@pop400.gsfc.nasa.gov, Lil Reichenthal <lreichen@pop700.gsfc.nasa.gov> X-CanltPRO-Stream: admin X-Spam-Score: 0 () X-Scanned-By: Canlt (www . canit . ca)

Ron,

1 1

Both Larry and myself agree with the decision to remove the two wires interconnecting the two boards to allow for ease of rework. And, later to reinstall at a later time in the PR instructions. Please red line your PR instructions (sign /date redline).

Thanks, Mike Jones APPENDIX 4: SEP LVPS TEST PROCEDURE

| Part Number            | Serial Number | Da            | te March 16,2005 |

|------------------------|---------------|---------------|------------------|

| Operator Selda Heavnes | Inspector     | Kan backson   | ~ 3-16-05        |

|                        |               | $\mathcal{U}$ |                  |

**APPENDIX 4:**

- No load current = 0,17A

- 5.1 Weight Measurement

5. Post-Conformal Coat Tests:

Weight: <u>N/A</u> grams 5.2 Functional tests Repeating Functional Test After PFR 1036

| Presence | of | Output | Voltages |

|----------|----|--------|----------|

|----------|----|--------|----------|

| Output Voltages           |        |        |        |      |

|---------------------------|--------|--------|--------|------|

| Signal name               | Mín    | Max    | Output | Unit |

| SEPT-NS 5.3 Digital       | 5.04   | 5.57   | 5.716  | V    |

| SEPT-NS 2.6 Digital       | 2.47   | 2.73   | 2.545  | V    |

| SEPT-NS 5.6 Analog        | 5.32   | 5.88   | 5.35   | V    |

| SEPT-E 5.3 Digital        | 5.04   | 5.57   | 5.336  | V    |

| SEPT-E 2.6 Digital        | 2.47   | 2.73   | 2.55   | V    |

| SEPT-E 5.6 Analog         | 5.32   | 5.88   | 5.71   | V    |

| SIT HET LET +13 Analog    | 12.35  | 13.65  | 13.40  | V    |

| SIT HET LET -13 Analog    | -13.65 | -12.35 | -13,5  | V    |

| SIT HET LET +6 Analog     | 5.70   | 6.30   | 5,9    | V    |

| SIT HET LET -6 Analog     | -6.30  | -5.70  | -6.17  | V    |

| SIT HET LET 2.6V Digital  | 2.47   | 2.73   | 2.52   | V    |

| SIT HET LET 3.4V Digital  | 3.23   | 3.57   | 3,319  | V    |

| SIT HET LET +5.1V Digital | 4.85   | 5.36   | 5.053  | V    |

| SIT HET LET -5.2V Digital | -5.46  | -4.94  | -5.16  | V    |

Efficiency This section will not be performed after PFR 1036

| Signal name              | Voltage | Current       | Power (W) |

|--------------------------|---------|---------------|-----------|

| SEPT-NS 5.3 Digital      |         | 1.2.11.2.2.2  | /         |